|

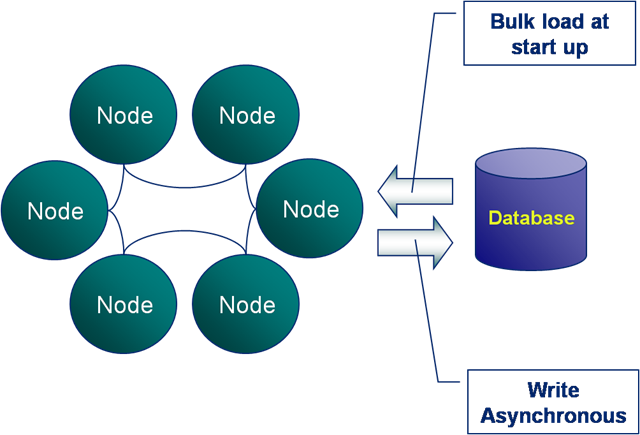

Multiprocessor systems use hardware mechanisms to implement low-level synchronization operations. Synchronization is a special form of communication where instead of data control, information is exchanged between communicating processes residing in the same or different processors. If an entry is changed the directory either updates it or invalidates the other caches with that entry. Here, the directory acts as a filter where the processors ask permission to load an entry from the primary memory to its cache memory. In a directory-based protocols system, data to be shared are placed in a common directory that maintains the coherence among the caches. This is the reason for development of directory-based protocols for network-connected multiprocessors. Broadcasting being very expensive to perform in a multistage network, the consistency commands is sent only to those caches that keep a copy of the block. However, when the copy is either in valid or reserved or invalid state, no replacement will take place.īy using a multistage network for building a large multiprocessor with hundreds of processors, the snoopy cache protocols need to be modified to suit the network capabilities. Read-hit − Read-hit is always performed in local cache memory without causing a transition of state or using the snoopy bus for invalidation.īlock replacement − When a copy is dirty, it is to be written back to the main memory by block replacement method. Then the local copy is updated with dirty state. This is done by sending a read-invalidate command, which will invalidate all cache copies. Write-miss − If a processor fails to write in the local cache memory, the copy must come either from the main memory or from a remote cache memory with a dirty block. When the shared memory is written through, the resulting state is reserved after this first write. If the new state is valid, write-invalidate command is broadcasted to all the caches, invalidating their copies. Write-hit − If the copy is in dirty or reserved state, write is done locally and the new state is dirty. In both the cases, the cache copy will enter the valid state after a read miss. If a dirty copy exists in a remote cache memory, that cache will restrain the main memory and send a copy to the requesting cache memory. If no dirty copy exists, then the main memory that has a consistent copy, supplies a copy to the requesting cache memory.

Read-miss − When a processor wants to read a block and it is not in the cache, a read-miss occurs. Cache Events and Actionsįollowing events and actions occur on the execution of memory-access and invalidation commands − By using write back cache, the memory copy is also updated (Figure-c). The write-update protocol updates all the cache copies via the bus. Invalidated blocks are also known as dirty, i.e. So, all other copies are invalidated via the bus. Processor P1 writes X1 in its cache memory using write-invalidate protocol. In this case, we have three processors P1, P2, and P3 having a consistent copy of data element ‘X’ in their local cache memory and in the shared memory (Figure-a). Write-invalidate and write-update policies are used for maintaining cache consistency. Snoopy protocols achieve data consistency between the cache memory and the shared memory through a bus-based memory system.

In general, there are three sources of inconsistency problem − When a write-back policy is used, the main memory will be updated when the modified data in the cache is replaced or invalidated. In this case, inconsistency occurs between cache memory and the main memory. If the processor P1 writes a new data X1 into the cache, by using write-through policy, the same copy will be written immediately into the shared memory.

In the beginning, three copies of X are consistent. Let X be an element of shared data which has been referenced by two processors, P1 and P2. Cache coherence schemes help to avoid this problem by maintaining a uniform state for each cached block of data.

For example, the cache and the main memory may have inconsistent copies of the same object.Īs multiple processors operate in parallel, and independently multiple caches may possess different copies of the same memory block, this creates cache coherence problem. In a multiprocessor system, data inconsistency may occur among adjacent levels or within the same level of the memory hierarchy. In this chapter, we will discuss the cache coherence protocols to cope with the multicache inconsistency problems.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed